# A Novel Sequence Switching Coding Scheme with L-Decoder Technique for Low Power Consumption in VLSI Design

<sup>1</sup> Ch. Likhitha, <sup>2</sup> Dr. Girija Sravani

<sup>1</sup>PG Students, <sup>2</sup>Associate Professor

1,2 Department of Electrical and Communication Engineering, K.L.U College of Engineering, Vijayawada, Andhra Pradesh, India

**Abstract:** Low power has become a critical design requirement in today's electronics industry, leading to a shift in focus where power dissipation is prioritized alongside performance and area. VLSI systems are now designed for high-speed operation with minimal area to ensure compact and reliable performance. Power optimization at the system level is an active area of research, especially concerning power dissipation in processing units, memories, and communication. A significant portion of power is consumed in data communication over on-chip and off-chip buses. To reduce power consumption, signal encoding techniques have been developed to minimize switching activity on buses, potentially saving up to 70% in power. One notable approach is the use of Hamming coding, such as the "Lagger algorithm," which minimizes transition power during bitsequence transmission by shuffling the bit streams before transmission and regenerating them using a decoder, effectively reducing transitions between 'o' and '1'

**Index Terms:** Power optimization, bit transition, lagger algorithm, hamming code, bus shuffling, bit streams

#### Introduction

The integration of devices in System On Chip (SOC) the issue of power consumption is increasing. There is a need to develop simpler and efficient low power coding scheme, which can reduce the power consumption at routing level and logical level. Though various techniques were developed to minimize the power consumption in logical devices the other power consumption approaches is also needed to be improved. In this work a focus is given towards minimization of power consumption in data transition time. For the evaluation of the developed approach the coding approach is integrated with an error coding approach to evaluate the minimization of power consumption in transition. The remainder of this paper is organized as follows. In Section II, presents the error coding technique used in the current low power coding approach.

In Section III, the approach of transition minimization is outlined. In Section IV, presents the digital modeling of the suggested approach in modular modeling. In Section V outlines the obtained simulation results obtained for the developed architecture and the timing simulation performed to verify the effectiveness of the proposed approach. Finally, in Section VI, some conclusions are drawn for the presentation of the suggested work.

### **Error Coding Technique**

Let assume E be the maximum number of error bits that the code can correct and D be the maximum number of error bits that it can detect, and in one error combination that strikes the system let ee, em, and ec be the number of errors in encoder, Digital word, and corrector. This fault secure detector can verify the correctness of the encoder and corrector operation. In any digital system the information bits are fed into the encoder to encode the information.

Vector and the fault secure detector of the encoder verify the validity of the encoded vector. If the detector detects any error, the encoding operation must be redone to generate the correct code word. Transient errors accumulate in the Digital words over time. In order to avoid accumulation of too many errors in the Digital words that surpasses the code correction capability, the system has to perform Digital scrubbing. Digital scrubbing is periodically reading Digital words from the device, correcting any potential errors and writing them back into the device

### **Transition Power Optimization Using Switch Logic**

Buses have been used as an efficient communication link among functional modules in very large scale integration (VLSI) systems. Whereas the size of functional modules decreases with the development of semiconductor technology, the size of VLSI chips increases, and so does the number of functional modules on a chip. Increasing communication requirements among the modules demand more complicated and more efficient buses

### **Switching Power Dissipation**

This is due to the charging and discharging of capacitive loads during logic changes. The dominant source of power dissipation is thus the charging and discharging of the node capacitances also referred to as the dynamic power dissipation.

The dynamic power dissipation and is given by:

$P=0.5CV_{\rm dd}^2(SW)f_{clk}$

Where C is the physical capacitance of the circuit, V<sub>dd</sub> is the supply voltage, E (SW) referred as the switching activity is the average number of transitions in the circuit per 1/f<sub>clk</sub> is the clock frequency.

A coding scheme called sequence-switch coding (SSC) is developed to reduce the transition power consumption in this work. It is different from previous transition-reduction coding schemes in that it is aimed at applications with the stream-type data transfer pattern.SSC reduces the number of bus transitions by rearranging the transmission sequence of data. An algorithm called switch algorithm is presented to show the feasibility of SSC. This algorithm reduces around 10% of bus transitions in transmission of the benchmark files. For the brevity

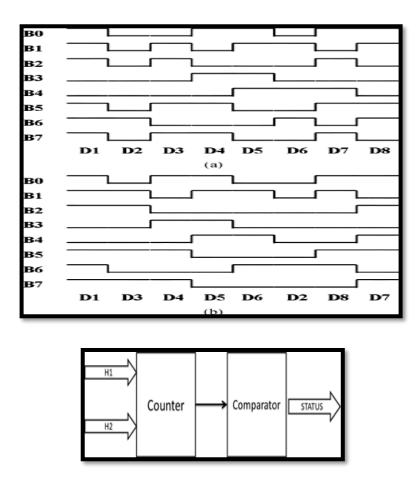

of description, let us define some terms and notations first. A switched sequence is defined as the sequence of words transmitted according to an SSC algorithm. Let us express the hamming distance between a word, W and a bus, B, as H (W; B). The waveforms of eight-bit bus for the eight data are transmitted by the (a) original order and (b) a different order. So far, most of the previous transition-reduction coding schemes have been developed for the granulated data, therefore, they have not considered the sequence of data as an important factor.

SSC is the first general- purpose coding scheme that employs the sequence of data in reducing the number of bus transitions. SSC needs no prior information on data to be sent, and it can be applied to any application that transmits more than two data sequentially for most operations.

**Figure 1:** Shows Illustration of the effect of transmission sequence on bus transitions (a) Original order (b) Different order

Let us assume that there are 8data to be sent via a bus figure 4.1(a) is the wave form of the bus, when these are transmitted without any modifications. If the data is sent with a different order example D1-D3- D4-D5-D6-D2-D8-D7, the wave from

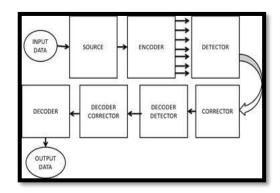

**Figure 2:** Shows illustrates the operational block diagram for the bus transition in imization using open switch Algorithm

Is changed as in figure in 4.1(b).the number of transitions with the new order is 23 compared to 32 with the original order. About 28 percent of bus changing only the transmission order reduces transitions .SSC, which is based on this observation, is a method intended to reduce the power consumption of busses by changing only the data segment

### **Design Implementation**

## **Bus Transition Optimization Technique**

For the optimization of power consumption during data transition a transition optimization for encoding and decoding architecture is developed. Figure illustrates the operational block diagram for the bus transition minimization using open switch Algorithm. The original information bits are passed to the encoding unit, after providing the error coding as explained in previous sections. These information bits are then coded for low transition logic to reduce the power consumption using the suggested switching logic approach as suggested above

The encoder unit consists of a comparator units and a counter unit for the generation of data stream during coding phase and shown in figure 2. The coding system reads the original data stream and code to generate equivalent coded streams passed as source data to the encoding unit. The source data in binary format is passed to the encoding unit in parallel format and are encoded using Hamming code distance for transition minimizations.

The transition minimization is carried with a parity code and is passed to the decoder for power consumption minimization. The internal functional units for the operation of the suggested architecture is as explained below.

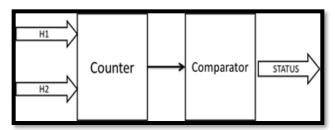

Figure 3: Shows illustrates the comparator units for the operation of bus transition selection using hamming code

The code comparator unit takes the three input data Din, Bus and Switch bus for the calculation of hamming distance for Switch and input data with data bus shown in figure 3.

**Figure 4:** Shows illustrates the code comparator unit

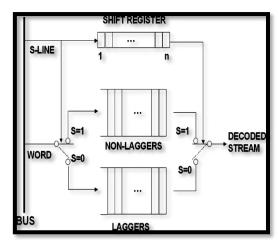

The decoder units with storage operation takes the hamming count and generates a count value based on the hamming distance passed the comparison is made and if the hamming distance is observed to be greater than the second value then status signal s=o is generated or else a '1 'is generated and shown in figure 4.4, the decoding operation of the designed system and the probable storage operation for the decoding operation for the decoding operation storing the segregated information for s='1' in digital location(mem1) and s='0' for digital location(mem2). Based on the digital location filled the data is segregated as block1 or block2 information.

**Figure 5:** Shows illustrates the Decoder unit with storage Operation

# **Algorithm for Transition Minimisation Steps As Follows**

- For the input data, the data sequence is rearranged to reduce the number of transitions that is hamming distance .The hamming distance means the number of transitions from'ı' to 'o' or ' o' to '1'.

- 2. If the hamming distance reduced then it will reduce the dynamic power consumption. The algorithm for less number of transitions is as follows.

- a) The data is rearranged to reduce the number of transitions.

- b) The hamming distance for each line is calculated

- c) For the entire data the total number of transition is calculated

#### Result

For the evaluation of the suggested approach an simulation is carried out in active HDL tool and synthesized using Xilinx ISE tool. The obtained simulation results are as shown below,

### **Timing Simulation Observation:**

The obtained simulation observations on performing write operation is as illustrated below

| Vane                     |                                 | Si.  | (m)            |              |   |      |   | 250.4 |     |     |       | · (0)                     | Vec      | 450     |           |         |

|--------------------------|---------------------------------|------|----------------|--------------|---|------|---|-------|-----|-----|-------|---------------------------|----------|---------|-----------|---------|

| = dout                   | 94                              |      | (iii           |              |   | (H   | _ |       | (6) | )28 | )ie   |                           | )EF      |         | (10       |         |

| R.S.                     | 1                               |      |                | ************ | - | www. |   |       | 1   | A   | _     |                           |          |         |           |         |

| ₱ ck                     | 0                               | Clo. |                |              |   |      |   |       |     |     |       |                           | <u> </u> |         |           | L       |

| ₱ tit                    | 0                               | R    |                |              |   |      |   |       |     |     |       |                           |          |         |           |         |

| o en                     | 1                               | (x1  |                |              |   |      |   |       |     |     |       |                           |          |         |           |         |

| * id_w                   | 1                               | (-1  |                |              |   |      |   |       |     |     |       |                           |          |         |           |         |

| e on                     | 00                              |      | (iii           |              |   |      |   |       |     |     |       |                           |          |         |           |         |

| = Lagger                 | 00                              |      | (w             |              |   |      |   |       |     | 94  | )8    |                           | )(98     |         |           |         |

| +B                       | W                               |      | (m             |              |   |      |   |       |     | (43 | )#    |                           | )/8      |         | )tr       |         |

| V+k                      | 1                               |      | (0             |              |   | _)(  |   |       |     |     | _)[_  |                           | )(4.     |         | )(        |         |

| o dn                     | uu                              |      | (II)           |              |   |      |   |       |     | (4) | )14   |                           | 78       |         | )tr       |         |

| = nl                     | Inn'on'on'on'on'on'             |      | (mmmmm)        | uu,uu)       |   |      |   |       |     |     |       |                           |          |         | )[ROUN    | uguju   |

| # n2                     | Inn'nn'nn'nn'nn'n               |      | (mananana)     | uuun -       |   |      |   |       |     |     |       |                           |          |         |           |         |

| =11                      | uu                              |      | (iii           |              |   |      |   |       |     |     | (9    |                           |          |         |           |         |

| m 12                     | UU                              |      | (iii           |              |   |      |   | 9     |     |     |       |                           | )(54     |         |           |         |

| = Diginal_data           | (09.32.34.09.34.85.50.34)       |      | (09,32,14,03,0 | A,B5,5C,3A)  |   |      |   |       |     |     |       |                           |          |         |           |         |

| # nodfed_data            | And nor nor nor nor nor nor not |      | Çununun        | DUMUUUU)     |   |      |   |       |     |     | )jese | हात्र्यसम्बद्धात <u>्</u> | Year.    | ppppppp | (mp.page) | מנפונים |

| ■ w modified_data        | niuu                            |      | (W             |              |   |      |   |       |     |     | )(IF  |                           | )(ir     |         | )(ir      |         |

| <b>■ # modified_date</b> | ntuu.                           |      | (III           |              |   |      |   |       |     |     | )(ir  |                           | )lir     |         | )(iii     |         |

| ■ modified_data          | 2/00                            |      | (UI)           |              |   |      |   |       |     |     | )(o   |                           | )(01     |         | )(iii     |         |

| ▼ modiled_data           | aluu                            |      | (0)            |              |   |      |   |       |     |     | )(iii |                           | )(iii    |         | yu.       |         |

| ¥ w modified data        | 4100                            |      | (UI)           |              |   |      |   |       |     |     | )(e   |                           | )(UI     |         | )(ut      |         |

| * * nodied_data          | 5(00                            |      | (in            |              |   |      |   |       |     |     | )le   |                           | )(in     |         | )(tř      |         |

| ■ wodfed data            |                                 |      | (w)            |              |   |      |   |       |     |     | )(1)  |                           | )(01     |         | )(in      |         |

| ● w modified_date        | 700                             | 1    | (iii           |              |   |      |   |       | -   |     | )(o   |                           | γίο      |         | χω.       | =       |

(a)

| Power | summary:  | 952233 |        |        | I (mA) | P (mW) |

|-------|-----------|--------|--------|--------|--------|--------|

| Total | estimated | power  | consum | ption: |        | 83     |

|       |           |        |        |        |        |        |

|       |           |        | Vecint | 1.20V: | 26     | 31     |

|       |           |        | Vccaux | 2.50V: | 18     | 45     |

|       |           |        | Vcco25 | 2.50V: | 3      | 7      |

|       |           |        |        |        |        |        |

|       |           |        | C      | locks: | 0      | 0      |

|       |           |        | I      | nputs: | 0      | 0      |

|       |           |        | 1      | Logic: | 0      | 0      |

|       |           |        | Out    | tputs: |        |        |

|       |           |        |        | Veco25 | 1      | 2      |

|       |           |        | 31     | gnals: | 0      | 0      |

|       |           |        |        |        |        |        |

|       | Quies     | cent 1 | Vecint | 1.20V: | 26     | 31     |

|       | Quies     | cent t | Vccaux | 2.50V: | 18     | 45     |

|       | Quies     | cent ' | Vcco25 | 2.50V: | 2      | 5      |

(b)

Figure 6: Shows (a) The simulation result for the developed routing power transition minimization (b) synthesis report

The obtained simulation result for the encoding system is as shown above. The error-coded information's are passed to the encoder unit where a switching scheme is developed for the minimization of transitions to reduce the transition power consumption

The modified data passed to the decoder after switch logic transition is shown in figure 6(a) above. It could be observed that the simulation result obtained after the decoding of received modified information is same as the original coded information. This illustrates the accuracy of the developed switch decoder logic after data bit switching. It illustrates the number of data transition seen for the given data which is observed to be reduced from 94 transitions to 49 transitions in the developed approach.

Once the decoded information is retrieved accurately the error decoding system is processed to retrieve the original information back based on the developed error decoding logic. The simulation clearly illustrates that the obtained data stream after the decoding logic is exactly the same as the original data sets. Synthesis Report is shown in figure 6 (b)

#### **Conclusion**

This work is focused towards the development of minimization of routing transition in digital circuitry. The developed approach is designed for power minimization for a coding system following error-coding algorithm. The operation of error coding is achieved via syndrome encoder and decoder approach and the coded information is evaluated for accuracy using the decoding logic developed. The approach of logical transition for the coded data is developed using open switch logic scheme. Where the coded data stream is passed is switched in an order to minimize transition based the code bit distance.

The developed system is observed to be accurate and provides about 50% lower transition to the original data transfer. The encoding and decoding approach for the developed system is tested for different data word bits and observed to be accurately recovering for up to half the data bit transition. The process of encoding and decoding operation is developed on VHDL.

#### References

- M. Alidina, J. Monteiro, S. Devadas, A. Ghosh, and M. Papaefthymiou." Precomputation- based sequential logic optimization for low power."In Proceedings of the 2019 International Workshop on Low Power Design, pages 57-62, April 1994.

- 2. W. C. Athas, L. J. Svensson, J. G. Koller, N. Thartzanis and E. Chou. "Low-Power Digital Systems Based on Adiabatic-Switching Principles." IEEE Transactions on VLSI Systems, 2(4)398-407:, December 2020

- 3. H. Bakoglu, Circuits, Interconnections, and Packaging for VLSI, Addison-Wesley, Menlo Park, CA, 2018

- 4. R. Horan et al. Idempotent, mattson-solomon polynomials and binary ldpc codes. IEE Proceedings of Communication, 153(2):256–262, 2010.

- 5. J. Kim et al. Error rate in current-controlled logic processors with shot noise. Fluctuation and Noise Letters, 4(1):83–86, 2004.

- 6. Donald E. Knuth. The Art of Computer Programming. Addison Wesley, second edition, 2000.

- 7. ShuLin and Daniel J. Costello. Error Control Coding. Prentice Hall, second edition,

2004.

- 8. R. J. Mc Eliece. The Theory of Information and Coding. Cambridge University Press, 2002.

- 9. Abdallah Saleh et al. Reliability of scrubbing recovery-techniques for memory systems. IEEE Transaction on Reliability, 39(1):114–122, 1990.

- 10. S. Chakravarty. "On the complexity of using BDDs for the synthesis and analysis of 28 Design Technologies for Low Power VLSI Boolean circuits". In Proceedings of the 27th Annual Allerton Conference on Communication, Control and Computing, pages 730-739, 1989.

- 11. Chandrakasan, S. Sheng, and R. W. Brodersen, "Low-power CMOS design." IEEE Journal of Solid-State Circuits, pages 472-484, April 1992.

- 12. Chandrakasan, M. Potkonjak, J. Rabaey and R.W. Brodersen, "HYPER-LP: A System for Power Minimization Using Architectural Transformation."In Proceedings of the I EEE International Conference on Computer Aided Design, pages 300-303, November 1992.